马上注册加入红色小队,结交更多好友,享用更多功能,让你轻松玩转社区。

您需要 登录 才可以下载或查看,没有帐号?立即注册

x

source:http://wccftech.com/amd-zen-architecture-hot-chips/ 本译文未经许可不得转载,严禁私自篡改标题、内容以及二次投递。

请支持独立网站,转发请注明本文链接:http://www.mykancolle.com/?post=397

前文:AMD Zen 微架构完全解析:双调度器,微指令缓存以及缓存架构

AMD在Hot Chips大会上展示了成吨的Zen架构细节。明年发布的Zen将专注于性能、吞吐量和能效的改善。凭借着Zen架构,AMD计划重返性能级CPU行列,冲击主流和发烧市场。

Zen架构完全解密 - 高并行度、高性能、高效率的核心设计

Zen基于GF 14nm FinFET制程,IPC相比Excavator提升了40%。

AMD在Hot Chips上的PPT揭露了完整的Zen架构细节

相比Carrizo和Godavari上的Excavator核心,大幅提升了IPC的Zen核心将会带来与Intel比肩的性能。实际上之前的渲染演示中,Zen已经比Brodwell-E 8核要略好了。

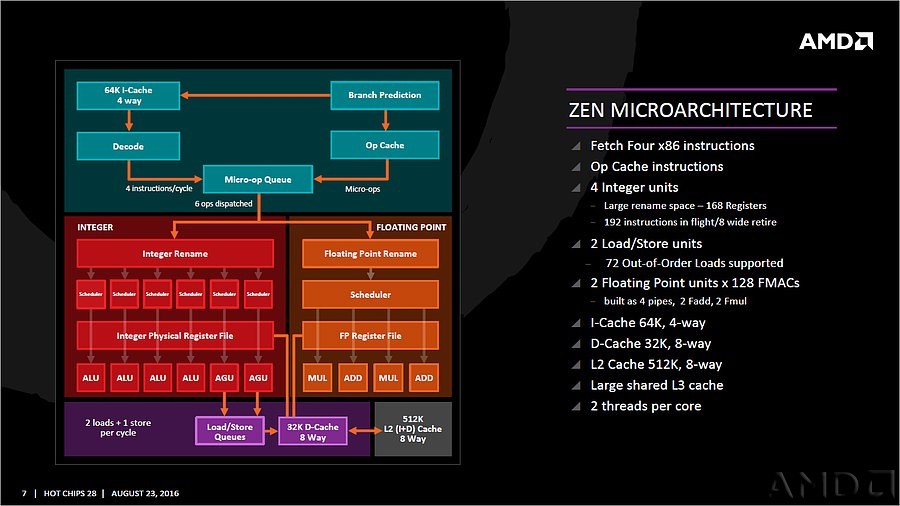

Zen核心设计

Zen的基本架构单元为CPU COMPLEX(CCX)。一个CCX内有4个核心,连接到同一块L3上。L3为16路关联,总共8MB容量,被分为4个区片,每个区片都有2片1MB的子区片,每个核心到达这些子区片的延迟都相同。

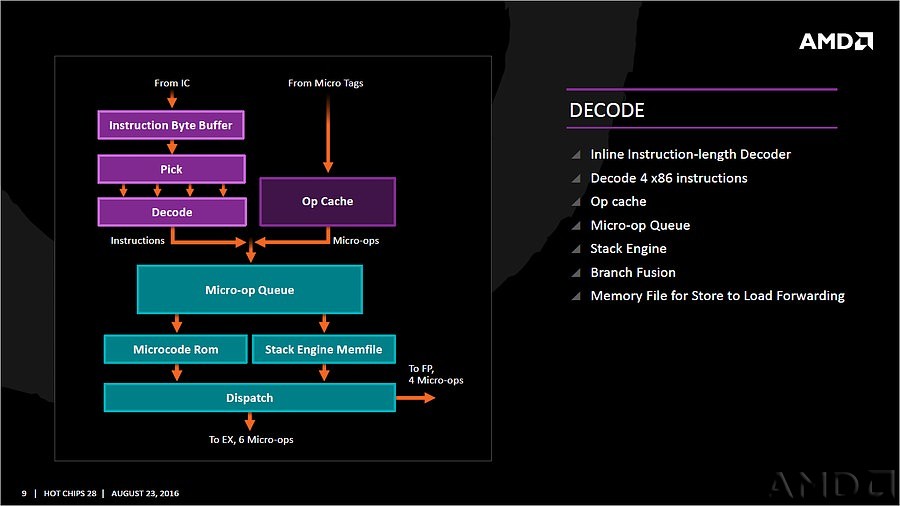

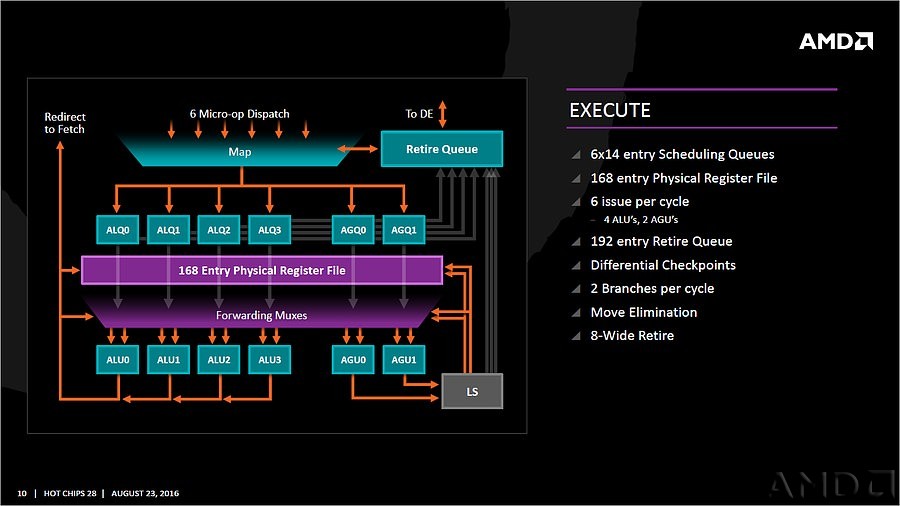

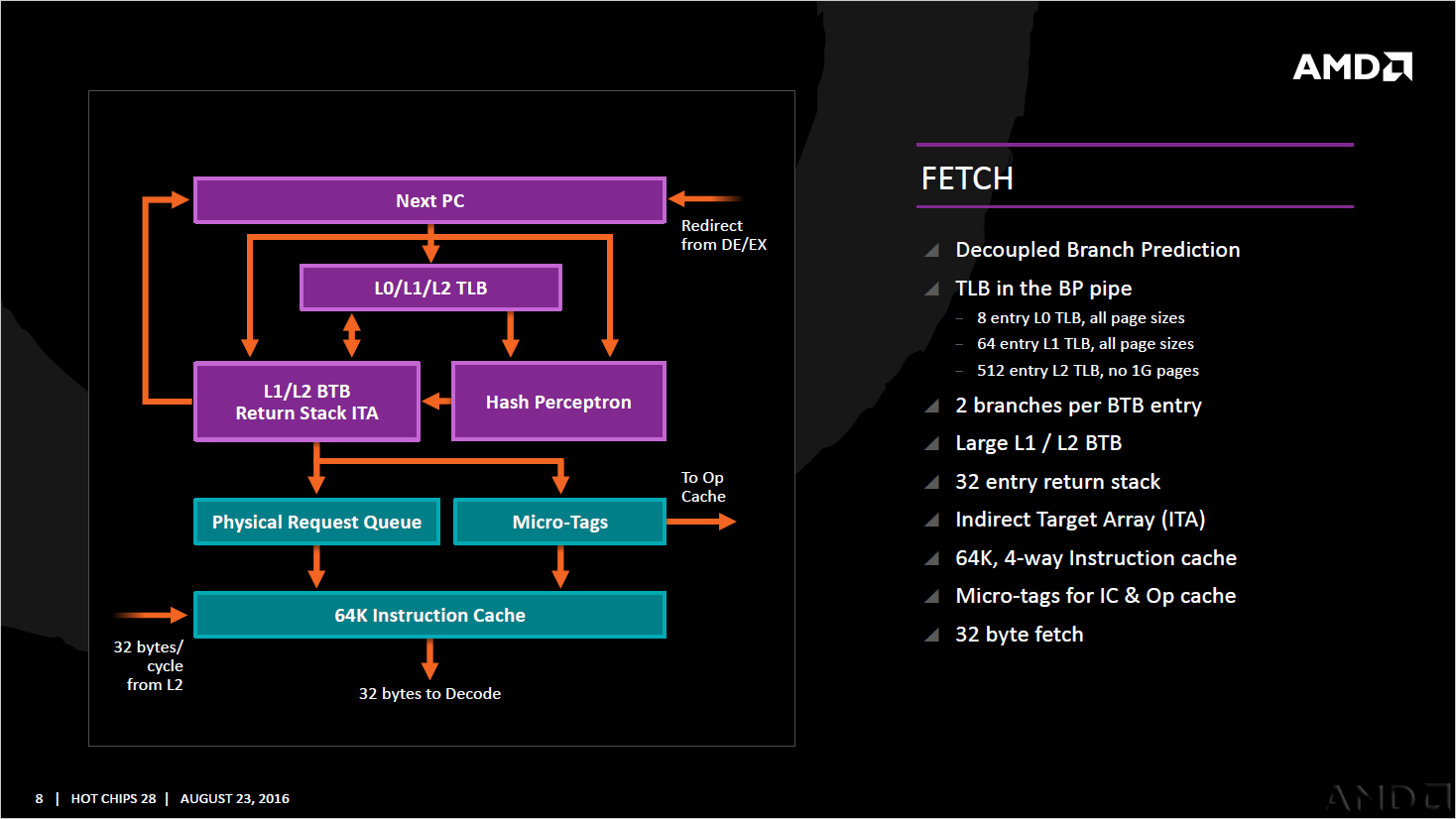

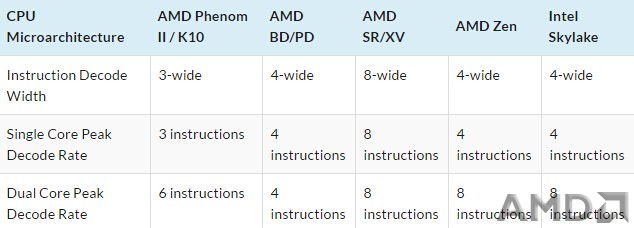

每个核心有2个线程。1个CCX为8线程,8核版本就有2个CCX,16线程。分支目标缓冲(branch target buffer,BTB)中每项变为两个分支,因此分支预测也大大改善。大容量微指令缓存能同时提升吞吐量和延迟。整数簇有6条管线,4个ALU,2个AGU。

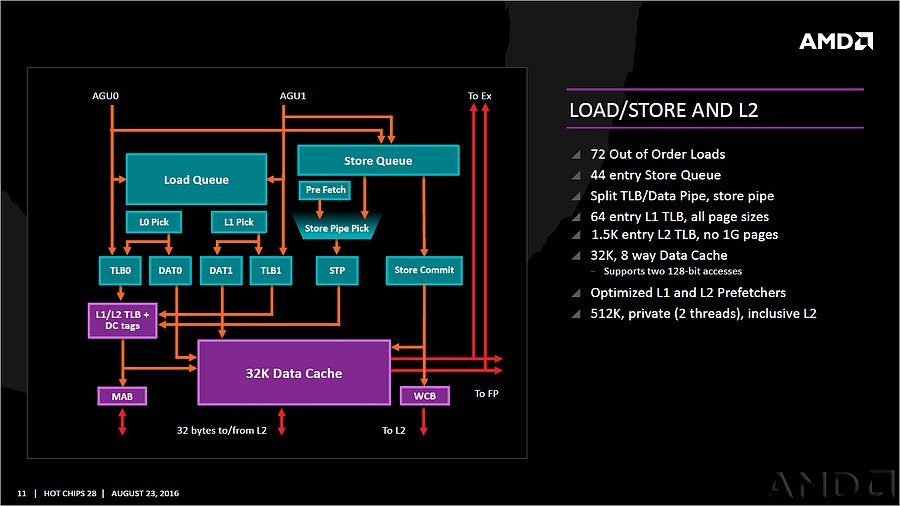

AGU每周可以进行2次16byte的load操作和1次16byte的store操作(通过32KB 8路组相连回写式L1数据缓存)。前文也有提到,从穿透式改为回写式可以显著减少特定情况下的闲置时间。Zen上的L/S缓存操作缓存的延迟也比Excavator更低。

Zen上的分发器为6条指令,比Excavator上的4条更大。整数和浮点单元的指令调度器也从84增加到了96.浮点单元现在是4发射了,退出、L/S操作的队列大小增加到了192、72、44,Excavator上为128、44、32。

两个浮点单元依然是4条管线,每个单元128bit FMAC。有两个计算用的FADD和两个FMUL单元。浮点单元继续使用2级调度队列,它的寄存器为160项,退出宽度为8,还有一条供128b store操作的管线。此外还有两个AES加密单元,兼容SSE,AVX1,AVX2,AES,SHA和MMX指令集。

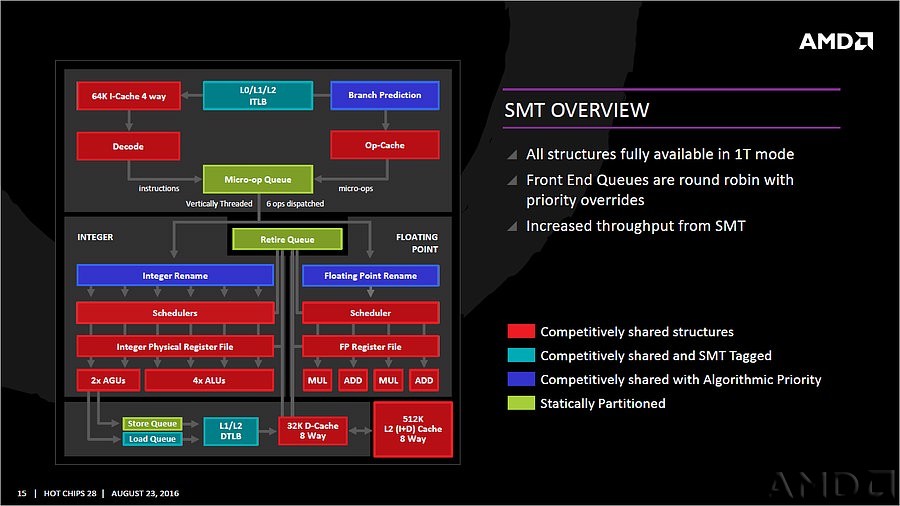

Zen的同步多线程

很多人早就预料到了Zen对同步多线程的支持。这使得Zen在设计层面上更加接近Intel。SMT设计能够通过同时执行两个线程来增加吞吐量,而且这两个线程在软件中都显示为独立核心。

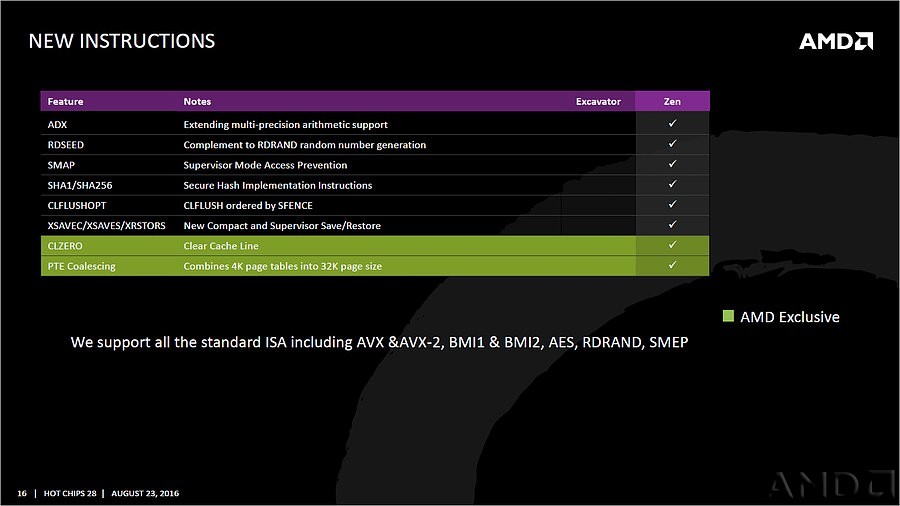

随着SMT的支持,Zen也增加了新指令。包括ADX,RDSEED,SMAP,SHA1,XSAVEC,CLZERO和PTE Coalescing。当然AMD也会支持上面提到的所有标准指令集。

Zen的高带宽,低延迟缓存系统

AMD一直都在谈论新核心上革新的缓存系统。这次细节终于透露出来了,缓存架构由每核心上的高速独立L2(512KB L+D 8路关联)和高速共享L3(8MB L+D 16路关联)组成。

这带来了缓存之间很高的带宽,使得预取性能提升。L3缓存主要被L2的victim占据,同时给L1和L2未命中带来更大的队列。

【注:victim的含义:Eviction驱逐

从cache移出一个line从而为新的数据腾出空间的过程我们成为Eviction。Eviction可以由用户发出的writeback-invalidate产生,被驱逐的line我们称为victim line。当victim line是dirty(“脏”)的时候,数据必须回写到下一级存储器中以维持内存的一致性。---来源http://blog.csdn.net/shanghaiqianlun/article/details/6945497】

每个核心还有64K L1 (4路关联)指令缓存和32KB L1 数据(8路关联)缓存。整个系统中更快的L1,L2,L3缓存能够使得FPU的load操作更快(需要7周期)。L1和L2带宽为原来的2倍,而L3带宽为5倍。

Zen - 14nmFinFET的 低功耗高性能设计

性能虽很重要,但AMD之前真正缺少的是能效。Zen上这种情况将会改变。Zen的能效比Excavator要高得多,而Excavator本身已经是高度优化过的架构。因为Zen上使用了激进的多层次多区块时钟门控技术。

Zen的低功耗特性

- 激进的多层次多区块时钟门控

- 写回式L1缓存

- 大容量微指令缓存

- 堆栈引擎

- Move Elimination【抱歉这个我不会翻译..】

- 从计划开始阶段就看重功耗

- 低功耗设计方法

|